Researchers from the University of Minnesota Twin Cities and a group from the National Institute of Standards and Technology (NIST) have created a ground-breaking method for creating spintronic devices that could end up as the new industry standard for semiconductors used in computers, smartphones, and many other electronic devices.

The new method will enable spintronic devices that can be scaled down and made smaller than ever before.

The researchers’ paper is published in Advanced Functional Materials, a peer-reviewed, top-tier materials science journal.

“We believe we’ve found a material and a device that will allow the semiconducting industry to move forward with more opportunities in spintronics that weren’t there before for memory and computing applications,” said Jian-Ping Wang, senior author of the paper and professor and Robert F. Hartmann Chair in the University of Minnesota Department of Electrical and Computer Engineering. “Spintronics is incredibly important for building microelectronics with new functionalities.”

Wang said Minnesota has been leading this effort in a big way for more than 10 years with strong support by the Semiconductor Research Corporation (SRC), Defense Advanced Research Projects Agency (DARPA), and the National Science Foundation (NSF).

This work is showing for the first time in the world that you can grow this material, which can be scaled down to smaller than five nanometers, on top of a semiconductor industry-compatible substrate, so-called CMOS+X strategies.

Deyuan Lyu

Along with numerous other patents connected to this research, Wang’s team has also collaborated with University of Minnesota Technology Commercialization and NIST to patent this technology. Additionally, this discovery offers up a fresh line of inquiry for the next ten years in the development and production of spintronic devices.

“This means Honeywell, Skywater, Globalfoundries, Intel, and companies like them can integrate this material into their semiconductor manufacturing processes and products,” Wang said. “That’s very exciting because engineers in the industry will be able to design even more powerful systems.”

The semiconductor industry is continually working to create ever-smaller chips so that electronic gadgets can have the highest possible levels of energy efficiency, processing speed, and data storage.

Traditional transistor-based chips are being replaced with spintronic devices, which use the spin of electrons to store data rather than the electrical charge. Additionally, these materials have the potential to be non-volatile, which means they consume less power and continue to function and store data long after their power source is turned off.

For more than a decade, spintronic materials have been successfully incorporated into semiconductor circuits; however, the scalability of the industry standard spintronic material, cobalt iron boron, has been reached. Engineers are now unable to create devices smaller than 20 nanometers without sacrificing their capacity for data storage.

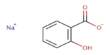

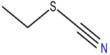

By demonstrating that iron palladium, a substitute for cobalt iron boron that uses less energy and has the potential for more data storage, can be scaled down to sizes as small as five nanometers, researchers from the University of Minnesota have found a way around this issue.

A unique piece of equipment among academic institutions nationwide and only accessible at the University of Minnesota, the 8-inch wafer-capable multi-chamber ultrahigh vacuum sputtering system allowed the researchers to grow iron palladium on a silicon wafer for the first time.

“This work is showing for the first time in the world that you can grow this material, which can be scaled down to smaller than five nanometers, on top of a semiconductor industry-compatible substrate, so-called CMOS+X strategies,” said Deyuan Lyu, first author on the paper and a Ph.D. student in the University of Minnesota Department of Electrical and Computer Engineering.

“Our team challenged ourselves to elevate a new material to manufacture spintronic devices needed for the next generation of data-hungry apps,” said Daniel Gopman, a staff scientist at NIST and one of the key contributors to the research. “It will be exciting to see how this advance drives further growth of spintronics devices within the semiconductor chip technology landscape.”

This research was funded by a $4 million, four-year grant from DARPA and in part by NIST; SMART, one of seven centers of nCORE, an SRC program; and NSF.

In addition to Wang, Gopman, and Lyu, the research team comprised University of Minnesota researchers across the College of Science and Engineering, including Department of Electrical and Computer Engineering researchers Qi Jia, William Echtenkamp, and Brandon Zink; Department of Mechanical Engineering researcher Dingbin Huang and Associate Professor Xiaojia Wang; and Characterization Facility researchers Javier García-Barriocanal, Geoffrey Rojas, and Guichuan Yu. National Institute of Standards and Technology researcher Jenae Shoup also contributed to the research.