Metastability

Definition

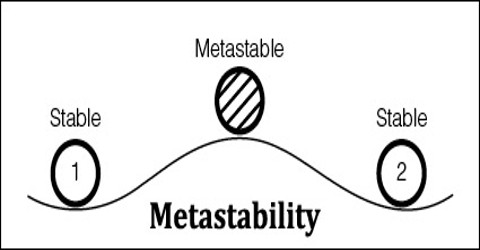

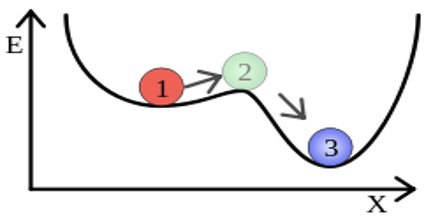

Metastability is the quality of a physical system that persists in its existing equilibrium when undisturbed or only slightly disturbed, but able to pass to a more stable equilibrium when sufficiently disturbed. A common example of metastability in science is isomerisation. Higher energy isomers are long lived as they are prevented from rearranging to their preferred ground state by (possibly large) barriers in the potential energy. It is common in physics and chemistry, from an atom to statistical ensembles of molecules at molecular levels or as a whole. The abundance of states is more prevalent as the systems grow larger and/or if the forces of their mutual interaction are spatially less uniform or more diverse.

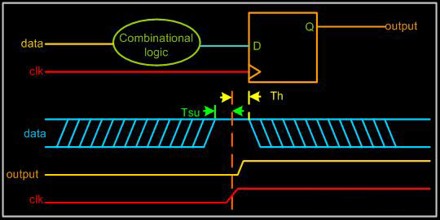

There are setup and hold time violations in any flip-flop, it enters a state where its output is unpredictable: this state is known as metastable state (quasi stable state); at the end of metastable state, the flip-flop settles down to either ‘1’ or ‘0’. This whole process is known as metastability. In the figure below Tsu is the setup time and Th is the hold time.

The metastability concept originated in the physics of first-order phase transitions. It then acquired new meaning in the study of aggregated subatomic particles, in atomic nuclei or in atoms or in molecules, macromolecules or clusters of atoms and molecules. Later, it was borrowed for the study of decision-making and information transmission systems.

Occurs of Metastability

Whenever setup and hold violation time occurs, metastability occurs, so we have to see when signals violate this timing requirement:

- When the input signal is an asynchronous signal.

- When the clock skew/slew is too much (rise and fall time are more than the tolerable values).

- When interfacing two domains operating at two different frequencies or at the same frequency but with different phase.

- When the combinational delay is such that flip-flop data input changes in the critical window (setup+hold window)

Ways to Minimize Metastability

Designers can tolerate metastability by making sure the clock period is long enough to allow for the resolution of quasi-stable states as well as whatever logic may be in the path to the next flip-flop. This approach, while simple, is rarely practical given the performance requirements of most modern designs.

It always stems from violating setup or hold times, which in turn comes from either poor design or asynchronous inputs. Every logic component takes time to propagate data. When a signal traverses many devices, the delays can add up significantly. If the data then goes to a latch, it’s quite possible that the delays may cause the input to transition at the same time as the clock. Instant metastability. Designers are generally pretty careful to avoid these situations, though.

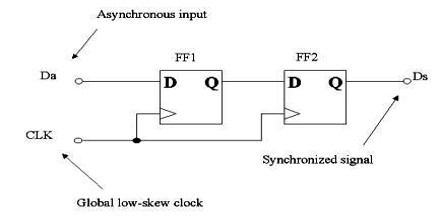

The most common way to tolerate metastability is to add one or more successive synchronizing flip-flops to the synchronizer. This approach allows for an entire clock period (except for the setup time of the second flip-flop) for metastable events in the first synchronizing flip-flop to resolve themselves. This does, however, increase the latency in the synchronous logic’s observation of input changes.

Reference: asic-world.com, vocabulary.com, wikipedia.